# Design and Implementation of High Speed Artificial Neural Network Based Sprott 94 S System on FPGA

Ismail Koyuncu \*1

Accepted 26th May 2016

DOI: 10.18201/ijisae.97824

*Abstract:* FPGA-based embedding system designs have been preferred for industrial applications and prototyping because of the advantages of parallel processing, reconfigurability and low cost. Due to having characteristic structure of the parallel processing of Artificial Neural Networks (ANNs), these systems provide the advantage of speed and performance when they are implemented with FPGA-based hardware. The hardware implementation of transfer functions used for modeling non-linear systems is a challenging problem. Therefore, this problem creates convergence problems. In this paper, non-linear Sprott 94 S system has been modeled using ANNs running on FPGA. All related parameter values and processes are defined with IEEE-754-1985 32-bit single precision floating-point number standard. ANN-based Sprott 94 S system design has been developed using VHDL synthesized using Xilinx ISE Design Tools. In test stage, ANN-based Sprott 94 S system has been tested using 3X100 data set and obtained error analysis results have been presented. The constructed design has been performed for Xilinx VIRTEX-6 family XC6VHX255T-3FF1923 FPGA chip using Place&Route process and chip usage statistics have been given. The clock frequency of ANN-based Sprott 94 S system which has pipeline processing scheme has been obtained with the value of 304.534 MHz. Accordingly, the proposed FPGA-based ANN system has produced 3X3.284 billion outputs in 1 second.

Keywords: FPGA, VHDL, Nonlinear Systems, ANN, Sprott 94 S System

# 1. Introduction

Currently, Field Programmable Gate Array (FPGA) chips have been used many areas since they have advantages like parallel processing, reconfigurablity, high speed comparable to other HardWare (HW) systems, possibility of the verification the designs by testing before the implementation of the HW, very low-cost than Application Specific Integrated Circuits (ASIC) HW for prototyping. Control [1], sensors [2], image processing [3], signal processing [4], converter systems [5], computer graphics [6], medicine [7], radio frequency systems [8], Artificial Neural Networks (ANNs) [9] are among the usage areas of FPGAs. ANNs, which are one of the research areas of FPGAbased HW, are parallel information processing systems in their nonlinear structure. These systems need speeding up the computational process in real time engineering applications. There are also other ways to implement the ANNs as HW: Digital Signal Processing (DSP) chips and ASIC. Once an ANN is implemented as an ASIC HW, the network configuration cannot be modified later. Since the DSP chip performs given tasks in a serial fashion, DSP chip implementations cannot exploit the parallelism in ANN applications. The Transfer Functions (TFs) that used in ANNs have been divided into two parts, namely linear and nonlinear [10]. Because of having exponential operations in nonlinear TFs, the implementation of these functions in HW could be difficult when high speed and precision are required. In this paper, high speed discrete-time ANN-based

<sup>1</sup>Department of Electronics and Automation, Duzce University, 81010, Duzce, Turkey

system has been modelled using FPGA chips. Logarithmic Sigmoid (LogSig) TF has been used for the hidden layer of ANNbased system. In the work, 32-bit single precision floating-point standard has been used and the system is coded with Very High Speed Integrated Circuit (VHSIC) Description Language (VHDL). In Section 2, general information about FPGA chips and ANNs have been given. In Section 3, the Sprott 94 S system has been presented. In Section 4, the structure and test process of the designed ANN-based discrete-time Sprott 94 S system on FPGA have been given. Besides, chip statistics and performance results obtained from implementation have been presented. Finally, the results of the study have been interpreted and some orientations have been announced for future work in Section 5.

# 2. General Information

## 2.1. FPGA Chips

FPGA chips, which provide flexibility in programmable systems using prebuilt resources, are high performance, reprogrammable and capable of parallel processing devices. Nowadays, these chips have various clock frequencies and HW features. IEEE-754-1985 64-bit, 32-bit or 16-bit floating-point and IQ-Math fixed point representations have been used in these chips by coding with VHDL, Verilog and Handle-C. Figure 1 shows Virtex-6 FPGA board produced by Xilinx. In general, FPGA chips consist of Input/Output-Blocks (I/O-Bs) that are dedicated to communicate with the outer world, Configurable Logic Blocks (CLBs) that perform logic functions and interconnects that can be programmable. CLBs contain Look up Tables (LUTs), multiplexers and flip-flop units [11].

<sup>\*</sup> Corresponding Author: Email: ismailkoyuncu@duzce.edu.tr

Figure 1. Xilinx Virtex-6 FPGA board

#### 2.2. Artificial Neural Networks

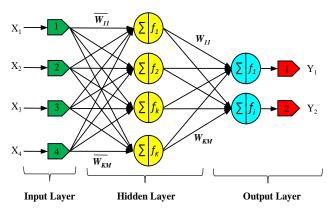

Recently ANNs are artificial intelligence structures developed for modelling nonlinear systems by mimicking the learning skills of human brain. ANN-based systems are utilized in numerous areas such as motors [12], control [13], medical [14], optimization [15, 16], signal-image processing [17, 18], prediction [19, 20]. TFs used in ANNs are divided into two parts: linear and nonlinear. While pure linear, positive linear, hard limiting, and symmetric hard limiting TFs are the examples of linear TFs, radial basis, logarithmic sigmoid and hyperbolic tangent sigmoid TFs are the examples of nonlinear TFs [21]. There are ANN structures like Feed Forward Neural Networks (FFNN), Recurrent Neural Networks (RNN) and Cascade-Correlation Neural Networks (CCNN) in literature. The structure of FFNN has been given in Fig. 2.

Figure 2. The structure of multilayer feed forward artificial neural network with one hidden layer

ANNs generally consist of three layers namely, an input layer, one hidden layer and an output layer. As the input layer accepts the input variables to ANN from environment, the output layer transmits the environment. The hidden layer is the section where the proposed nonlinear system is modelled using neuron cell mathematically. Each artificial neuron consists of five parts namely inputs, weights, bias, TF and output.

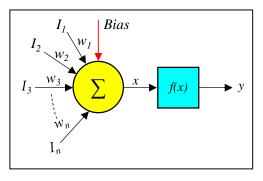

The general structure of neuron has been presented in Figure 3. Firstly, the input data  $I_1, I_2,...,I_n$  are multiplied with their corresponding weights  $w_1, w_2,...,w_n$  and then summed together. If the neuron has bias value then the x value has been reached by summing the obtained value with the bias value. The result has been fed in the transfer function and the obtained value; y has been transferred to the output.

Figure 3. The general structure of neuron with bias

#### 3. The numerical model of Sprott 94 S system

In general, chaotic systems are described with differential equations. The differential equations for Sprott 94 S [22] nonlinear autonomous system are given in Equation (1). In this equation,  $\alpha$  and  $\beta$  are the system parameters and x, y and z are dynamic variables of this system. The variations in system parameters have changed the dynamic characteristic of the system [23]. For this reason, these parameters are quite important for determining the system behaviour. The Sprott 94 S system is simulated with the system parameters of  $\alpha$ =-4.0 and  $\beta$ =1.0. The initial conditions of the system have been set  $x_0$ = $y_0$ = $z_0$ =0.05 for producing chaotic signals. The system is described by the following nonlinear Equation (1):

$$dx/dt = -x(t) - \alpha \cdot y(t)$$

$$dy/dt = x(t) + z(t)^{2}$$

$$dz/dt = x(t) + \beta$$

(1)

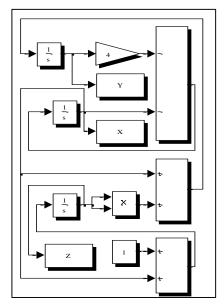

The numeric simulation of the system has been executed using **Mat**rix **Lab**oratory (Matlab)-Simulink software for extracting the phase portrait of Sprott S system. The numeric simulation model of the system is presented in Figure 4.

Figure 4. The Matlab-Simulink model of Sprott S system

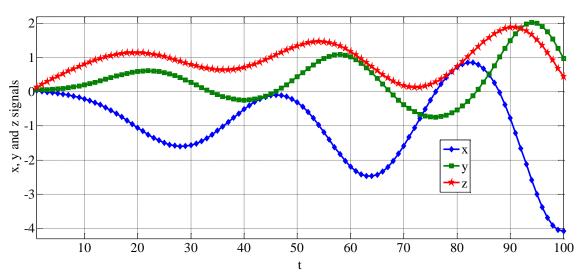

The output graphic of Sprott S system obtained from Matlab-Simulink model is given in Figure 5. In addition, phase portraits of Sprott 94 S system were displayed in performing numerical simulation, as shown in Figure 5 for parameters of  $\alpha = -4.0$  and  $\beta = 1.0$  and initial conditions  $x_0 = y_0 = z_0 = 0.05$ . As shown in Figure, the system exhibits chaotic behaviour.

Figure 5. Sprott 94 S system: x, y and z time series and phase portraits obtained from Matlab-Simulink modeling results: x-y phase portrait, x-z phase portrait and y-z phase portrait

## 4. Discrete-Time ANN Based Implementation of Sprott 94 S System on FPGA

In this work, ANN-based Sprott 94 S system has been modelled using Matlab for implementing the discrete-time of the system on FPGA. For the ANN-based Sprott 94 S system, the structure of Feed Forward Multi-Layer Neural Network has been used. ANNbased system has 3 inputs and 3 outputs, respectively and pureline transfer function has been used for the output layer. The hidden layer has 7 neurons consisting Logarithmic Sigmoid (LogSig) transfer function which is one of the nonlinear transfer functions realized difficult by HW 10,000 samples have been generated by using fifth order Runge-Kutta-Butcher (RK-5-B) algorithm [24]. The generated samples have been divided into two groups: 8,000 samples for training and 2,000 samples for the test process. 100,000 epochs have been defined in training process with Levenberg-Marquardt (LM) algorithm. At the end of the training, the performance value (Mean Square Error (MSE)) has reached 2.30E-13. After the performed training and test processes, FPGA-based ANN has been evaluated using the obtained values of weight and bias coded inVHDL.

In the presented work, Look-Up-Table (LUT) and COordinate Rotation DIgital Computer (CORDIC) based approximations [25] have been united for the implementation of LogSig transfer function used in the hidden layer of ANN on FPGA. The calculations between the values of  $-\pi/4-\pi/4$  in other words  $e^{0.7853981}$ - $e^{-0.7853981}$  are possible using the values of Sinh(x) and Cosh(x) generated by CORDIC unit. In the proposed work, the received values to transfer function can be calculated between  $e^{-48}$  and  $e^{+47.25}$  using CORDIC-LUT-based approximation.

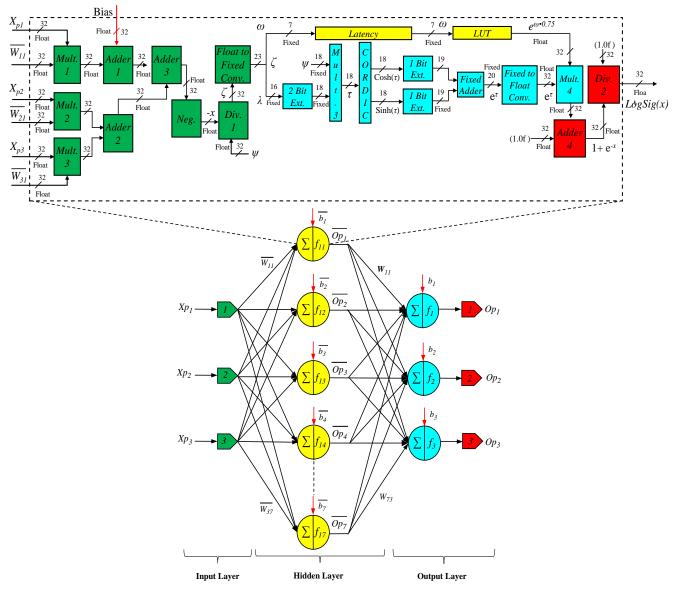

In Figure 6, the neuron structure used in hidden layer and FPGAbased multilayer feed-forward ANN structure have been given. The input values of  $X_{p1}$ ,  $X_{p2}$  and  $X_{p3}$  have been multiplicated by the corresponding weight values  $\overline{W_{11}}$ ,  $\overline{W_{21}}$  and  $\overline{W_{31}}$  using the units of *Mult1*, *Mult2* and *Mult3* on FPGA. Since these operations have parallel and pipeline processing scheme, the result of the first multiplication has been summed with the bias value for avoiding the latency process. Then, the obtained value by summing two intermediate values has been transmitted to LogSig transfer function.

The value of -x signal has been obtained with negation process for LogSig transfer function. After that, the obtained value has been divided by  $\psi = 0.75$  for degrading the value to be calculated by CORDIC unit and the obtained  $\psi$  value has been converted to fixed point number standard. The fractional  $(\lambda)$  and integer  $(\omega)$ parts of the  $\psi$  value have been separated each other by transmitting to two pipeline channels. After the latency process,  $e^{\omega}$  value which corresponds to  $\omega$ , has been obtained from LUT. In the second pipeline part, the calculation of  $\lambda$  value has been performed using CORDIC, taken  $\psi \ge \lambda$  into consideration. In here, first of all 2-bits have been added to the most significant bit (MSB) of  $\lambda$  (16-bit) for compability of  $\psi$  (18-bit). Then, the obtained value  $\lambda$  has been multiplied by  $\psi$  to send result value,  $\tau$ to CORDIC unit.  $sin(\tau)$  and  $cos(\tau)$  have been transmitted to adder unit by calculating them in CORDIC unit. In there,  $e^{\tau}$  value has been obtained by summing these two signals and has been sent to multiplier unit by converting to float-point standard. Then, the values of  $e^{\tau}$  and e  $\omega$  have been multiplicated to reach  $e^{-x}$  value.  $e^{-x}$ value has been summed with FP 1.0 value and the transfer function value of LogSig(x) has been calculated by dividing the obtained value into FP 1.0 value (in 32-bit single precision IEEE-754-1985 floating-point number standard).

Figure 6. The neuron structure of hidden layer and FPGA-based Sprott 94 S system feed forward-multilayer ANN

ANN-based Sprott 94 S system on FPGA has been coded with VHDL. 32-bit IEEE-754-1985 single precision floating-point number standard has been used in the implementation. The Place&Route process has been performed by synthesizing with Xilinx ISE Design Tools (DTs) 14-1 simulation program for Xilinx Virtex–6 family XC6VHX255T-3FF1923 chip. The statistical parameters of clock speed and FPGA chip utilization summary have been investigated and given in Table 2. Furthermore the minimum pulse period of ANN-based Sprott 94 S system has been obtained 3.284 ns using Xilinx ISE DTs 14-1 simulation program.

The discrete time series results of x, y and z of the presented ANN-based Sprott 94 S system obtained from the implementation on Virtex-6 FPGA chip using Xilinx ISE DTs have been shown in Figure 7. Just after 137 clock cycle, ANN-based Sprott 94 S system produces the first outputs. After the first outputs, system outputs have been produced once per a 137 clock cycle. Although 32-bit IEEE-754-1985 floating-point number standard has been used in the design, the simulation results of Xilinx ISE Design Tools 14-1 have been shown in Hexadecimal number standard to examine the discrete time series of x, y and z more comfortable.

|          |          | r        |        |          | - ~ p==== > ~ ~ ~ ~ ~ |            |  |  |

|----------|----------|----------|--------|----------|-----------------------|------------|--|--|

| Xilinx   | Slice    | DSP48E1s | LUTs   | Occupied | Bounded               | Max. Clock |  |  |

| FPGA     | Register | Number   | Number | Slices   | IOBs                  | Frequency  |  |  |

| Chip     | Number   |          |        | Number   | Number                | (MHz)      |  |  |

| VIRTEX-6 | 75,551   | 7        | 76,308 | 23,278   | 195                   | 304.534    |  |  |

| %        | 23       | 1        | 48     | 61       | 40                    |            |  |  |

Table 1. FPGA chip utilization summary for the ANN-based Sprott 94 S system

|                    |          | <u>1,676.417 ns</u> |          |       |         |                         |         |   |      |         |       |          |        |         |                         |       |              |         |              |

|--------------------|----------|---------------------|----------|-------|---------|-------------------------|---------|---|------|---------|-------|----------|--------|---------|-------------------------|-------|--------------|---------|--------------|

| Name               | Value    |                     | 1,650 ns | 1     | 1,660 n | ns<br>I I I I I I I I I | 1,670 n | s |      | 1,680 n | s<br> | 1,690 ns |        | 1,700 n | ns<br>I I I I I I I I I | 1,710 | ns<br>IIIIII | 1,720 n | IS           |

| 🕨 📲 ann_in1[31:0]  | c0814c7e |                     |          |       |         |                         |         |   |      |         |       |          |        |         |                         |       |              |         |              |

| 🕨 👹 ann_in2[31:0]  | 3fa2a47e |                     |          |       |         |                         |         |   |      |         |       |          |        |         |                         |       |              |         |              |

| 🕨 👹 ann_in3[31:0]  | 3f2e1aea |                     |          |       |         |                         |         |   |      |         |       |          |        |         |                         |       |              |         |              |

| 🗓 cik              | 1        |                     |          |       |         |                         |         |   |      |         |       |          |        |         |                         |       |              |         |              |

| 👍 reset            | 0        |                     |          |       |         |                         |         |   |      |         |       |          |        |         |                         |       |              |         |              |

| Ug start           | 1        |                     |          |       |         |                         |         |   |      |         |       |          |        |         |                         |       |              |         |              |

| 🕼 ready            | 1        |                     |          |       |         |                         |         |   |      |         |       |          |        |         |                         |       |              |         |              |

| ▶ 🔩 ann_out1[31:0] | bc133c00 | 0000                | 0000     | ) 3cf | 30200   | 3c2                     | 234000  | X | bc13 | 3c00    | ) bce | e5c00    | bd4d   | 9c00    | bd96                    | 9600  | ) bdc        | ef00    |              |

| ▶ 🔩 ann_out2[31:0] | 3d828100 | 0000                | 0000     | X 3d5 | ed600   | ) 3d                    | 6ff200  | X | 3d82 | 8100    | X 3d9 | 03400    | X 3da7 | 8300    | X 3dc2                  | 6100  | ) 3de        | 5e 100  |              |

| ▶ 🔩 ann_out3[31:0] | 3e972680 | 0000                | 0000     | X 3e0 | 8=600   | ) 3e                    | 5cde00  | X | 3e97 | 2680    | X 3el | f8800    | X 3ee6 | c900    | 3f06                    | 6980  |              | 7440    | $\mathbf{X}$ |

| 🛯 clk_period       | 10000 ps |                     |          |       |         |                         |         |   |      |         |       |          |        |         |                         |       |              |         |              |

Figure 7. ANN-based Sprott 94 S system dicrete time series on FPGA

The binary values of the designed ANN-based Sprott 94 S system in 32-bit single precision IEEE–754-1985 floating-point number standard related to x, y and z discrete time signals obtained the implementation on Virtex-6 FPGA chip using Xilinx ISE DTs 14-1 have been saved in a file during the simulation test process. After the conversion of the saved values to the real number system, the discrete time series produced by ANN-based Sprott 94 S system using the first 3x100 data set have been presented in Figure 8.

Figure 8. The discrete time series of ANN-based Sprott 94 S system designed on FPGA using Xilinx ISE Design Tools 14-1

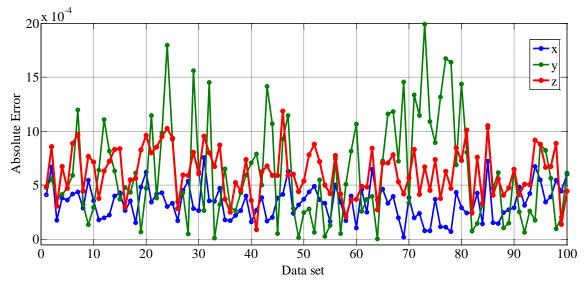

The error analyses of Mean Squared Error (MSE), Root Mean Squared Error (RMSE), Normalized Mean Squared Error (NMSE), Mean Absolute Error (MAE) and Mean Absolute Percentage Error (MAPE) have been performed to specify the error rate of FPGA-based design constructed for ANN-based Sprott 94 S system using IEEE-754-1985 32-bit single precision floating-point number standard. RK5-Butcher algorithm has been selected as a reference in the performed error analyses studies and the first 3x100 data set generated from ANN-based Sprott 94 S system on FPGA has been used. The results of the obtained analyses have been presented in Table 2.

Furthermore, absolute error analysis results of ANN-based Sprott 94 S system implemented on FPGA have been presented graphically in Figure 9. According to obtained results, the minimum error value of *y* 2.37623E-06 and maximum error value of *y* 1.98885E-03 have been observed for 3X100 data set generated by ANN-based Sprott 94 S system.

| Table 2. MSE. RMSE. | NMSE MAE and | MAPE analysis of     | ANN-based St | prott 94 S system on F | FPGA |

|---------------------|--------------|----------------------|--------------|------------------------|------|

| Table 2. Mol, RMDL, |              | wir ii L anarysis Or | Thin Oasea D | prou 24 o system on r  | 10/1 |

|         |           | •         |           | •         | •         |

|---------|-----------|-----------|-----------|-----------|-----------|

| Signals | MSE       | RMSE      | NMSE      | MAE       | MAPE      |

| <br>X   | 1.369E-07 | 3.699E-04 | 1.231E-07 | 3.416E-04 | 2.148E-03 |

| У       | 5.991E-07 | 7.740E-04 | 1.383E-06 | 6.253E-04 | 3.285E-03 |

| z       | 4.314E-07 | 6.568E-04 | 2.172E-06 | 6.191E-04 | 9.921E-04 |

|         |           |           |           |           |           |

Figure 9. The absolute error analysis results of ANN-based Sprott 94 S system implemented on FPGA

### 5. Conclusion

In the presented work, nonlinear Sprott 94 S system has been modelled using the approximation of LogSig transfer function on FPGA. The performed modelling of ANN's architecture has been developed using VHDL with IEEE-754-1985 32-bit single precision floating-point arithmetic. The design of ANN-based Sprott 94 S system has been synthesized using Xilinx ISE Design Tools and tested using 3X100 data set. The error analysis results related to obtained tests have been presented. The performed design has been implemented with the Place&Route process for Xilinx VIRTEX-6 family, XC6VHX255T-3FF1923 FPGA chip and chip utilization statistics have been given. The ANN-based Sprott 94 S system having pipeline processing scheme on FPGA can be used with a clock frequency up to 304.534 MHz and ANN-based system has produced 3X3.284 billion outputs in 1 s. As further work, different nonlinear systems can be modelled using FPGA-based ANNs. Thus the performance and error analysis can be performed using obtained results. In future, embedded secure communication applications can be performed using the proposed ANN-based Sprott 94 S system on FPGA.

#### References

- H. H. Chiang, K. C. Hsu and I. H. Li (2015). Optimized adaptive motion control through an SoPC implementation for linear induction motor drives. IEEE/ASME Transactions on Mechatronics. Vol. 20(1). Pages. 348–360.

- [2] Y. Yue, S. W. Feng, C. S. Guo, X. Yan and R. R Feng (2015). All-digital thermal distribution measurement on field programmable gate array using ring oscillators. Microelectronics Reliability. Vol. 55(2). Pages. 396–401.

- [3] E. Tlelo-Cuautle, V. H. Carbajal-Gomez, P. J. Obeso-Rodelo, J. J. Rangel-Magdaleno and J. C. Nuñez-Perez (2015). FPGA realization of a chaotic communication system applied to image processing. Nonlinear Dynamics. Vol. 82(4). Pages. 1879–1892.

- [4] Ö. Polat and T. Yıldırım (2010). FPGA implementation of a general regression neural network: an embedded pattern classification system. Digital Signal Process. Vol. 20. Pages. 881–886.

- [5] M. Milanovic, M. Truntic, P. Slibar and D. Dolinar (2007).

Reconfigurable digital controller for a buck converter based on FPGA. Microelectronics Reliability. Vol. 47(1). Pages. 150–154.

- [6] I. Sahin (2011). A 32-bit floating-point module design for 3D graphic transformations. Scientific Research Essay. Vol. 5(20). Pages. 3070–3081.

- [7] J. X. Wu, C. H. Lin, Y. C. Du, P. J. Chen, C. C. Shih and T. Chen (2010). Estimation of arteriovenous fistula stenosis by FPGA based Doppler flow imaging system. 2015 IEEE International Symp. In Ultrasonics (IUS). Pages. 1–4.

- [8] J. Vanhamel, D. Fussen, E. Dekemper, E. Neefs, B. Van-Opstal, D. Pieroux and P. Leroux (2015). RF-driving of acoustic-optical tunable filters; design, realization and qualification of analog and digital modules for ESA. Microelectronics Reliability. Vol. 55(9). Pages. 2103–2107.

- [9] M. Alçın, İ. Pehlivan, and İ. Koyuncu (2016). Hardware design and implementation of a novel ANN-based chaotic generator in FPGA. Optik-International Journal for Light and Electron Optics. Vol. 127(13). 5500-5505.

- [10] M. T. Hagan, H. B. Demuth and M. Beale (2002). Neural network design. Thomson Learning Press. ISBN-10: 7111108418.

- [11] I. Koyuncu, A. T. Ozcerit and I. Pehlivan (2014). Implementation of FPGA-based real time novel chaotic oscillator. Nonlinear Dynamics. Vol. 77. Pages. 49–59.

- [12] X. Yang, J. Cao and D. W. Ho (2014). Exponential synchronization of discontinuous neural networks with time-varying mixed delays via state feedback and impulsive control. Cognitive Neurodyn. Vol. 9. Pages. 113–128.

- [13] J. Fei and H. Ding (2012). Adaptive sliding mode control of dynamic system using RBF neural network. Nonlinear Dynamics. Vol. 70. Pages. 1563–1573.

- [14] D. Avci, M. K. Leblebicioglu, M. Poyraz and E. Dogantekin (2014). A new method based on adaptive discrete wavelet entropy energy and neural network classifier (ADWEENN) for recognition of urine cells from microscopic images independent of rotation and scaling. Journal Medicial Systems. Vol. 38(2). Pages. 1–9.

- [15] S. L. Ho and Y. Shiyou (2012). A fast robust optimization methodology based on polynomial chaos and evolutionary algorithm for inverse problems. IEEE Transactions on Magnetics. Vol. 48(2). Pages. 259–262.

- [16] C. J. Lin, H. M. Tsai (2008). FPGA implementation of a wavelet neural network with particle swarm optimization learning, Math. & Comp. Modell. Vol. 47. Pages. 982–996.

- [17] O. L. Savkay, V. Tavsanoglu, M. E. Yalcin and E. Cesur (2015). Computer assisted sperm analysis system designed on a hybrid CPU+ FPGA architecture. 23th IEEE Signal Processing and Communications Applications Conference (SIU). Pages. 1425–1428.

- [18] V. Paukštaitis and A. Dosinas (2009). Pulsed neural networks for image processing. International Journal of Electronics and Electrical Eng. Vol. 7. Pages. 15–20.

- [19] H. Papadopoulos and H. Haralambous (2011). Reliable prediction intervals with regression neural networks. Neural Networks. Vol. 24. Pages. 842–851.

- [20] M. Kanayama, A. Rohe and L. A. Paassen (2014). Using and improving neural network models for ground settlement prediction. Geotechnical and Geological Engineering. Vol. 32. Pages. 687–697.

- [21] S. Haykin (1999). Neural networks a comprehensive foundation. Prentice Hall.

- [22] J. C. Sprott (1994). Some simple chaotic flows. Physical Review E. Vol. 50(2). Pages. 647–650.

- [23] Ü. Çavuşoğlu, A. Akgül, S. Kaçar, İ. Pehlivan and A. Zengin (2016). A novel chaos-based encryption algorithm over TCP data packet for secure communication. Security and Communication Networks. DOI: 10.1002/sec.1414.

- [24] S. Senthilkumar and A. Piah (2012). An improved fuzzy cellular neural network (IFCNN) for an edge detection based on parallel Runge-Kutta (5, 6) approach. International Journal of Computational Systems Engineering. Vol. 1(1). Pages. 70–78.

- [25] İ. Sahin and İ. Koyuncu (2011). FPGA çipleri için CORDIC Tabanlı exp(x) hesaplama ünitesi tasarımı. e-Journal of New World Sciences Academy. Vol. 6(4). Pages. 1565–1572.