# ESKİŞEHİR TEKNİK ÜNİVERSİTESİ BİLİM VE TEKNOLOJİ DERGİSİ B- TEORİK BİLİMLER

Eskişehir Technical University Journal of Science and Technology B- Theoretical Sciences

2020, 8(2), pp. 247 - 256, DOI: 10.20290/estubtdb.633238

# A COMPREHENSIVE DETERMINING OF CAPACITANCE -VOLTAGE PARAMETERS OF ELECTRONIC DEVICES WITH METAL AND *p*-Si JUNCTION

# Fatih Mehmet COŞKUN <sup>1,\*</sup> 问

<sup>1</sup>Istanbul Medeniyet University Faculty of Engineering and Natural Sciences, Engineering Physics Department, TR-34700 Istanbul, Turkey

# ABSTRACT

Al-*p*-Si-Al structures were fabricated and temperature dependent capacitance versus voltage measurements were performed in this study. The Al contacts were grown by the sputtering method and then capacitance-voltage characteristics of the devices were performed with forward and reverse biases. According to this measurements, the  $C^{-2}-V$  plots were conducted. With the help of those calculation, the barrier height vs temperature ( $\Phi_{CV}-T$ ), the carrier concentration vs temperature ( $N_A - T$ ) and the depletion width vs temperature (w - T) graphs were plotted. In conclusion, it has been seen that the  $\Phi_{CV}$  and wdecreased, and  $N_A$  almost remained constant with increasing temperature.

Keywords: Heterojunctions, Capacitance-Voltage, Barrier Height

# **1. INTRODUCTION**

The devices with metal-semiconductor junctions are one of the important electronic circuit components in the electronic industry. These devices are commonly made by using metals like Ni, Au, Al etc. and semiconductor substrates like Si, GaAs, InP etc. [1 - 2]. The interface between the metal/semiconductor (MS) shows a rectifying property and this is a very critical point in industries like optoelectronic and switching technology [3]. In this interface layer there exists a barrier height (BH) and the characteristics of the semiconductor device are generally depend on this diode parameter [4]. Today, Schottky barrier formation at the MS junction still atracts attention in the field of semiconductor devices [5].

In the literature there are variety of examples of experimental studies of barrier heights in MS systems. Among the Schottky barrier height (SBH) measurement methods, the capacitance–voltage (C-V) method is one of the most convenient and common method, by which the built-in potential V<sub>bi</sub> can be drived from the extrapolation of the intercept in the x- axis, which is "voltage", in the straight line of  $C^2 - V$  curve [6]. In order to perform this extrapolation, the carrier concentration inside the structure is usually accepted to stay stable. Besides, in other cases – namely in the cases of unstable doping concentration, which may be the result of ion embedding, diffusion of carriers, unexpected impurities [7 - 8] or tendency to change in the temperature [9] - this method is not suitable, since the  $C^2 - V$  curves show nonlinear characteristics. According to some reports in the literature, this method was still applied in a range around 0 V in order to eliminate those undesired consequences [9 - 11]. However, when zero bias temperature dependent barrier heights are tried to be calculated from  $C^2 - V$  measurements, it is seen that the value of the barrier height changes with temperature gradient and this situation is generally attributed to the change in the crystal form at the MS interface [12 - 13].

The purpose of this paper is to determine and interpret the temperature dependent change of characteristics metal-Si device parameters such as the barrier height  $\Phi_{CV}$ , the carrier concentration N<sub>A</sub> and depletion width *w*, and furthermore the temperature dependent change of *C*–*V* and *C*<sup>2</sup>–*V* curves.

<sup>\*</sup>Corresponding Author: <u>fatihmehmetcoskun@gmail.com</u> Received: 15.102019 Published: 31.08.2020

Another important parameter at the MS contacts is the carrier concentration and under temperature gradient it is expected to be constant because of the linearity of  $C^2-V$  curve [14]. However it may demonstrate a deviation from the linearity especially at low temperatures [15], and may decrease sharply. On the other hand, the depletion width at the MS contact is expected to be decreased by increasing carrier concentration [6, 16]. In this paper, we report a MS device fabrication and the SBH, carrier concentration and the depletion region width from C-V measurements.

## 2. MATERIALS AND METHODS

According to the Si wafer cleaning procedures in the literature [17], the semiconductor crystal - Si was chemically dipped in CP-4 (HF:CH<sub>3</sub>COOH:HNO<sub>3</sub>; 1:1:2) solution at least 3 min initially, and then was exposed to HF:H<sub>2</sub>O (1:15) mixture to eliminate the oxidized layer on the substance surface. After this cleaning procedure a tiny Al film was groved on the matt surface of *p*-Si by thermal evaporation method. The Al coated *p*-Si substrate was annealed at 570 °C for 3 min under the gas flow of argon inside a furnace. Then, Al was evaporated on the shadow mask with holes (about 1 mm) and dot Schottky junctions were fabricated on the front of *p*-Si as seen from the figure 1. By those procedures, the Al/p-Si/Al Schottky diodes were formed.

Figure 1. (Color online) The illustrative model of the Al/p-Si/Al diodes

The C-V measurements of fabricated metal –Si rectifying device was conducted through ARS 4K closed cycle helium (He) cryostat, which has LakeShore 330 temperature controller with 0.2 K step, between 40-320 K temperatures using Boonton 72B capacitance meter. The depletion capacitance calculations were achieved from the following formula [6, 21];

$$\frac{1}{C^2} = \frac{2\left(\Phi_{CV} - V_p - V\right)}{q\varepsilon_s N_A A^2} \tag{1}$$

In equation (1),  $\Phi_{CV}$  is the barrier height according to C-V measurements and  $V_p$  stands for the difference electrical potential between the Fermi level and the valance band maximum in the neutral region of *p*-type semiconductor and it is expressed by the equation

$$V_p = kT \ln\left(\frac{N_v}{N_A}\right) \tag{2}$$

where  $N_v$  is the state density in the valance band [6, 20] and it is calculated using the carrier concentration  $N_A$ , which can be drived from the slope of the linear  $C^2$  - V plot at each measurement temperature. The carrier concentration  $N_A$  can be attained from the derivative of equation (1) as follows;

$$N_A = \frac{2}{q\varepsilon_0 A^2} \frac{dV}{d(C^{-2})} \tag{3}$$

$(\Phi_{CV} - V_p) = V_{D0}$  in equation (1) gives the diffusion potential,  $V_{D0}$ , at the zero bias and it can be calculated from the extrapolation of the linear part of  $C^{-2}-V$  curve to the V axis. So we may give the equation (1) as;

$$\frac{1}{C^2} = \frac{2(V_{D0} - V)}{q\varepsilon_s N_A A^2}$$

(4)

In this simplest form of depletion layer capacitance per unit area formula, the expression in the numerator can be written as  $2(V_{D0} + V)$  according to the applied voltage. Also,  $\varepsilon_s$  is the permittivity of the semiconductor, q is the electronic charge and A is the diode area in equation (1). According to those formulas, the capacitance to voltage (C-V), C<sup>-2</sup> to V, Barrier height to temperature ( $\Phi_{CV}$ -T), carrier concentration to temperature ( $N_A$ -T) and depletion width to temperature (w-T) plots were conducted.

#### 3. RESULTS AND DISCUSSION

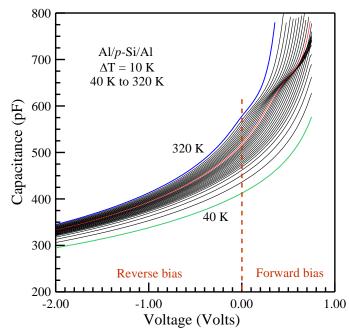

Figure 2 demonstrates the experimental *C-V* measurement results of the Schottky rectifier junction with a structure of Al-*p*-Si-Al in the temperature range of 40-320 K with 10 K steps. The *C-V* measurements were made at high frequency of 500 kHz, to prevent the contribution of the interface state charges and trap levels to the diode capacitance [6,9,16]. Therefore, this anomalous behavior observed in C-V results of Schottky diodes (SDs) has been generally ascribed to the presence of interface layer effects and series resistance  $R_s$  (between the space charge region and the Al contact) of the neutral region of the semiconductor body [23-28]. On the other hand, the series resistance  $R_s$  also plays an important role while shaping the *C-V* characteristics of the SDs, and causes them to be different from those that would be expected [23-28].

Figure 2. (Color online) Forward and reverse bias capacitance-voltage characteristics for the Al/p-Si/Al diode with steps of 10 K at 500 kHz

It has been stated in some investigations that there exists an abnormal peak in forward C-V characteristics [23-28]. The origin of such peak has been referred to the interface states by Ho et al. [23], and to the series resistance effect by Chattopadhyay et al. [25-28] and Chattopadhyay [28]. As expected, at high forward bias voltage there is always a deviation of the ideality in the C-V curves that has been definitely claimed to be the result of interfacial state density and series resistance in device.

That is, the presence of the  $R_s$  appears an anomalous in the forward bias *C-V* characteristics, and also turns out such a strange voltage dependence of the capacitance. Therefore, the forward bias capacitance measurements were made up to 1.0 Volt. The reason for this is not to observe the capacity peak which appears from the series resistance effect and interface states at high voltages.

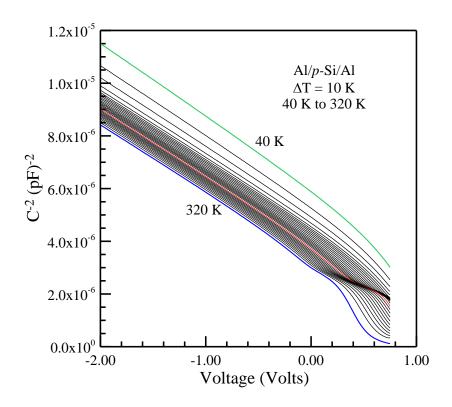

The  $C^2$  to V plot at reverse and forward bias at each temperature is shown in the Fig. 3. The  $C^2$  to V curves at reverse bias at each temperature especially are used to determine the parameters such as the barrier height, carrier concentration, diffusion potential and depletion width. As seen from the figure, at reverse bias portion of  $C^2$  to V curves at each temperature, the graph shows almost a linear behavior. However at about zero bias there exist a fluctuation and deviation from linearity in the graph. This may be the result of the carrier concentration behavior [22].

Figure 3. (Color online) Forward and reverse bias C<sup>2</sup> - V characteristics for the Al/p-Si/Al diode with steps of 10 K at 500 kHz

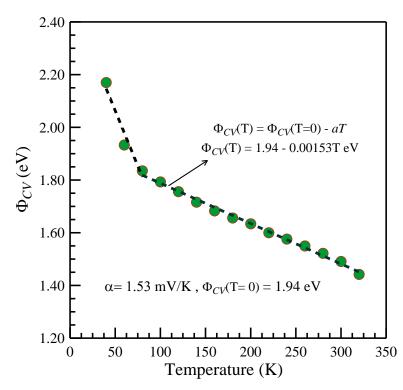

Barrier heights of the device according to varying temperature is given in the Fig. 4. If a barrier height is temperature depended – like our samples – it can be expressed as:

$$\Phi_{CV}(T) = \Phi_{CV}(T=0) - \alpha T \tag{5}$$

Where  $\Phi_{CV}(T = 0)$  is the BH at zero temperature and  $\alpha$  is the temperature coefficient of the barrier hegiht [3]. Since  $\alpha$  is the slope, it can be calculated from the graph and it is 0.00153 V/K.  $\Phi_{CV}$  can be calculated by a simple modulation in the expression:

Coşkun / Eskişehir Technical Univ. J. of Sci. and Tech. B – Theo.Sci. 8 (2) – 2020

$$(\Phi_{CV} - V_p) = V_{D0} \tag{6}$$

$$\Phi_{CV} = V_{D0} + V_p \tag{7}$$

with the help of eqn. (2).

$$\Phi_{CV} = V_{D0} + kT \ln\left(\frac{N_v}{N_A}\right) [6, 21]$$

(8)

The values of  $\Phi_{CV}$  in Fig. 4 was calculated from eqn. (8) and the graph was plotted according to these values. As can be seen from Fig. 4, According to the fit equation  $\Phi_{CV} = 1.94$  -0.00153T eV to the partion in 100 K-320 K range of the curve,  $\Phi_{CV}$  at zero temperature is 1.94 eV. Here,  $\alpha$  is the temperature coefficient.

Figure 4. (Color online) Barrier height versus temperature plot from the C<sup>-2</sup> - V curves for the Al/p-Si/Al diode

In figure 4, the temperature constant of the BH, that were attained from the experimental results, is seen as  $\alpha = -1.53 \text{ meV/K}$  for the Al/*p*-type Si SD and this is too far from the temperature coefficient value - which was -0.24 meV/K - of the energy gap for Si given in ref. [29] and [30] from temperature coefficient of the barrier height reported for Si semiconductor by some authors [20,30, 32]. For example, it was stated that the BH temperature coefficient value is -0.121 meV/K for PtSi/*p*-Si by McCaffrty et al. [20]. Also by Aboelfotoh and Tu [31] the so called values are found in the range of (-0.128) - (-0.147) meV/K for Ti/*p*-Si and TiSi<sub>2</sub>/*p*-Si and by Karatas et al. it was -0.247 meV/K for hydrogen terminated *p*-type Si. Those differences can be attributed to the formation of an oxide layer between Si and Al metal. Known conventionally, there exists an oxide region on a Si surface regardless of wafer cleaning processes whether it was etched with diluted HF or not [33-37]. Furthermore, the Si surface is usually coated with a thin insulating layer, if Si wafers are polished by

## Coşkun / Eskişehir Technical Univ. J. of Sci. and Tech. B – Theo.Sci. 8 (2) – 2020

ordinary methods and etched by chemicals, and if the metal is evaporated in a traditional vacuum chamber under a pressure of almost  $10^{-5}$  torr. The thickness of this oxide layer may be between 10 and 30 Å depending on the Si wafer preparation process. Interface layers may also be encountered in relation to the exposure of water or vapour onto the surface of the wafer before placing the evaporation chamber [25-27,33-39]. The Metal-Si contacts fabricated under those conditions are not perfect neighbouring contacts because of the insulating interfacial layer in the order of atomic dimensions [25-27,33-39]. For a satisfactory insulating layer, the interface states are in steady contact with the semiconductor and they do not keep in touch with the metal [25-27,33-39]. Therefore, the dielectric constant value ( $\epsilon_i$ ) of the interfacial layer should not be very different from the value for bulk SiO<sub>2</sub> [25-27,33-39].

Also, one can see figure 4 that the barrier height decreases with the increasing temperature. This characteristic is in close agreement with the results that were stated in the literature which says that the barrier height is inversely proportional to the temperature in Si [40, 41]. According to Aboelfotoh [40], Crowell et al. [41] and Cola et al. [42] this behaviour can be associated with the band gap of Si and the decrease in the carrier concentration around the space charge region [43].

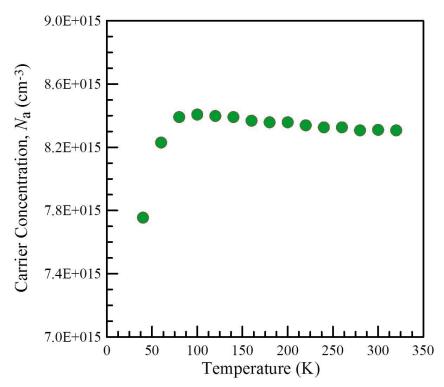

The  $N_A$  against temperature plot is demonstrated in Fig. 5. As seen from the figure, the carrier concentration approximately shows a very slight increase from 320 K to 80 K and then decreases sharply.

Figure 5. (Color online) Carrier concentration versus temperature plot from the C<sup>-2</sup> - V curves for the Al/p-Si/Al diode

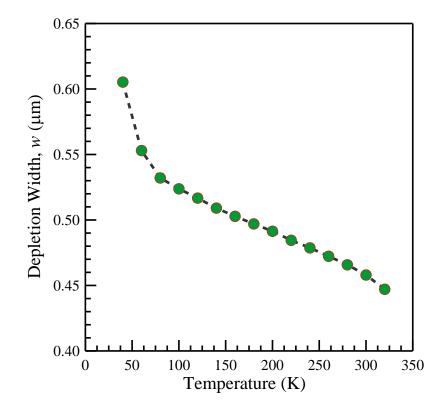

Finally the depletion width versus temperature graph can be seen from Fig. 6. From the graph it can be seen that the depletion width shows an almost lineer behavior from 320 K to 80 K, and then sharply makes a curvature and increases with a bigger slope. The sharp increase at 80 K may be attributed to the decrease in carrier concentration at this temperature.

Figure 6. (Color online) Depletion width versus temperature plot from the  $C^{-2}$  - V curves for the Al/p-Si/Al diode

## **4. CONCLUSION**

In this study, Al Schottky contacts were fabricated by the sputtering method over *p*-Si-Al substrates and forward and reverse bias temperature dependent capacitance versus voltage measurements were conducted. With the help of those measurements depletion layer, the capacitance were calculated and  $C^2$  vs V graph was plotted. With basic calculations, Barrier height vs temperature ( $\Phi_{CV}$  vs T), the carrier concentration vs temperature ( $N_A$  vs T) and the depletion width vs temperature (w vs T) graphs were done. In conclusion it has been seen that - with increasing temperature - the  $\Phi_{CV}$  decreases,  $N_A$ remains constant and w decreases.

## ACKNOWLEDGEMENTS

The author would like to express his sincere thanks to Prof. Abdulmecit Türüt and Prof. Hasan Efeoğlu for their many valuable contributions.

## REFERENCES

- [1] Mönch W. Metal-semiconductor contacts: electronic properties. Surface Science 1994; p. 928-944.

- [2] Türüt, A and Köleli, F. Metallic polythiophene/inorganic semiconductor Schottky Diodes. Physica B, 1993; 192: 279-283.

- [3] Çaldıran Z, Deniz AR, Aydoğan Ş, Yeşildağ A, Ekinci D. The barrier height enhancement of the Au/n-Si/Al Schottky barrier diode by electrochemically formed an organic Anthracene layer on n-Si. Superlattices and Microstructures. 2013; 56: 45-54.

- [4] Çaldıran Z, Deniz AR, Şahin Y, Metin Ö, Meral K and Aydoğan Ş. The electrical characteristics of the Fe<sub>3</sub>O<sub>4</sub>/Si junctions. J. Alloys and Comp. 2013; 552: 437-442.

- [5] Li, JG. Energetics of metal/ceramic interfaces, metal-semiconductor Schottky contacts, and their relationship. Materials Chemistry and Physics. 1997; 47: 126-145.

- [6] Sze SM. Physics of Semiconductor Devices. 2nd ed. New York, USA: John Willy & Sons, 1981.

- [7] Decker DR. Measurement of Epitaxial Doping Density vs. Depth. Journal of Electrochem. Soc. 1968; 115: 1085.

- [8] Thomas CO, Kahng D and Manz RC. Impurity Distribution in Epitaxial Silicon Films. Journal of Electrochem. Soc. 1962; 109: p.1055.

- [9] Sağlam M and Türüt A. Effect of thermal annealing in nitrogen on the I-V and C-V characteristics of Cr-Ni-Co alloy/LEC *n*-GaAs Schottky diodes. Semicond. Sci. Technol. 1997; 12: p.1028-1031.

- [10] Wang L. and Nathan MI. High barrier height GaN Schottky diodes: Pt/GaN and Pd/GaN. Appl. Phys. Lett. 1996; 68: p.1267.

- [11] Schmitz AC, Ping AT, AsifKhan M, Chen Q, Yang JW and Adesida I. Metal contacts to n-type GaN. Journal Electronic Mat. 1998; 27: p. 255.

- [12] Kubota N, Ao JP, Kikuta D and Ohno Y. Schottky Barrier Height Determination by Capacitance-Voltage Measurement on n-GaN with Exponential Doping Profile. Jpn. J. Appl. Phys. 2004; 43: p.4159.

- [13] Werner, JH and Güttler HH. Temperature dependence of Schottky barrier heights on silicon J. Appl. Phys. 1993; 73: p.1315.

- [14] Saxena V, Jim JN and Steckel AJ. High-Voltage Ni– and Pt–SiC Schottky Diodes Utilizing Metal Field Plate Termination. IEEE Transactions On Electron Devices, 1999; 46-3.

- [15] Karataş Ş, Altındal Ş, Türüt A and Özmen A. Temperature dependence of characteristic parameters of the H-terminated Sn/p-Si(1 0 0) Schottky contacts. App. Surface Sci. 2003; 217: p.250-260.

- [16] Türüt A, Yalçın N and Sağlam M. Parameter Extraction From Non-Ideal C-V Characteristics of A Schottky Diode With and Without Interfacial Layer. Solid-State Electronics 1992; Vol. 35, No. 6: p. 835-841.

- [17] Kern, W. The Evolution of Silicon Wafer Cleaning Technology. Journal of Electrochem. Soc. 1990; Vol. 137, No. 6: p.1887.

- [18] Mönch W. Semiconductor Surfaces and Interfaces, 2nd ed. Berlin, Germany: Springer, 1995.

- [19] Sze SM and Kwok KN. Physics of Semiconductor Devices, 3rd ed. Hoboken: Wiley & Sons, Inc., 2006.

- [20] Mccafferty PG, Sellai A, Dawson P and Elabd H. Barrier Characteristics of PtSi/p-Si Schottky Diodes. Solid-State Electronics 1996; 39: 583-592.

- [21] Van der Ziel A. Solid State Physical Electronics. 2nd ed. Englewood Cliffs, NJ: Prentice-Hall, 1968.

- [22] Aydoğan Ş, Sağlam M and Turut A. Some electrical properties of polyaniline/p-Si/Al structure at 300 K and 77 K temperatures. Microelectronic Engineering 2008; 85: 278–283.

- [23] Ho PS, Yang ES, Evans HL and Wu X. Electronic states at silicide-silicon interfaces. Phys. Rev. Lett. 1986; 56: 177.

- [24] Werner J, Levi AFJ, Tung RT, Anzlower M, and Pinto M. Origin of the excess capacitance at intimate Schottky contacts. Phys. Rev.Lett. 1988; 60: 53.

- [25] Chattopadhyay P and Raychaudhri B. Origin of the anomalous peak in the forward capacitancevoltage plot of a Schottky barrier diode. Solid-State. Electron. 1992; 35: 875.

- [26] Chattopadhyay P and Raychaudhri B. New technique for the determination of series resistance of Schottky barrier diodes. Solid-State. Electron. 1992;35: 1023.

- [27] Chattopadhyay P and Raychaudhri B. Frequency dependence of forward capacitance-voltage characteristics of Schottky barrier diodes. Solid-State Electron. 1993;36: 605.

- [28] Türüt A, Yalçın N and Sağlam M. Parameter extraction from non-ideal C–V characteristics of a Schottky diode with and without interfacial layer. Solid-State Electron. 1992; 35: 835.

- [29] Zhu S, Van Meirhaeghe RL, Detavernier C, Ru GP, Li BZ, Cardon F. A BEEM study of the temperature dependence of the barrier height distribution in PtSi/n-Si Schottky diodes. Solid-St Comm. 1999; 112: 611.

- [30] Aboelfotoh MO. Electrical characteristics of Ti/Si(100) interfaces. J. Appl. Phys. 1988; 64: 4046.

- [31] Aboelfotoh MO and Tu KM. Schottky-barrier heights of Ti and TiSi<sub>2</sub> on n-type and p-type Si(100). Phys. Rev. B 1986; 34: 2311.

- [32] Karataş Ş, Altındal Ş, Turut A, Özmen A. Temperature dependence of characteristic parameters of the H-terminated Sn/p-Si(1 0 0) Schottky contacts. Appl. Surf. Sci. 2003; 217: 250.

- [33] Rhoderick EH. The physics of Schottky barriers. J. Phys. D: Appl. Phys. 1970; 3: 1153.

- [34] Chattopadhya P and Daw AN. On the current transport mechanism in a metal—insulator semiconductor (MIS) diode. Solid-State Electron. 1986; 29: 555.

- [35] Fonash SJ. A reevaluation of the meaning of capacitance plots for Schottky-barrier-type diodes. J. Appl. Phys. 1983; 54: 1966.

- [36] Card HC and Rhoderick EH. Studies of tunnel MOS diodes II. Thermal equilibrium considerations. J. Phys. D Appl. Phys. 1971; 4: 1602.

Coşkun / Eskişehir Technical Univ. J. of Sci. and Tech. B – Theo.Sci. 8 (2) – 2020

- [37] Singh A. Characterization of interface states at Ni/*n*CdF<sub>2</sub> Schottky barrier type diodes and the effect of CdF<sub>2</sub> surface preparation. Solid-State Electron. 1985; 28: 223.

- [38] Rhoderick EH. Metal-Semiconductor Contacts, (Oxford University Press, 1978) p.121, 136.

- [39] Türüt A, Sağlam M. Determination of the density of Si-metal interface states and excess capacitance caused by them. Physica B, 1992; 179: 285.

- [40] Aboelfotoh MO. Temperature Dependence of The Schottky-Barrier Height of Tungsten on *n*-Type and *p*-Type Silicon. Solid-State Electronics. 1990; 34: No:1 53.

- [41] Crowell CR, Sze SM and Spitzer WG. Equality of The Temperature Dependence of The Gold-Silicon Surface Barrier and The Silicon Energy Gap In Au *n*-type Si Diodes. Applied Physics Letters. 1964; 4: 92.

- [42] Cola A, Vasanelli L and Muret P. A Method For The Determination of Barrier Heights From The Capacitance-Voltage Characteristics of A Schottky Junction Containing Bulk Deep Traps. Solid-State Electronics. 1995; Vol. 38, No. 5: 989-995.

- [43] Karabulut A. Barrier height modification in Au/Ti/n-GaAs devices with a HfO<sub>2</sub> interfacial layer formed by atomic layer deposition. Bull. Mater. Sci. 2019; 42:5.