www.dergipark.gov.tr ISSN:2148-3736

El-CezerîJournal of ScienceandEngineering Vol: 10, No: 1, 2023 (81-89) DOI :10.31202/ecjse.1162711

## **Research Paper**

# Design of Power and Area Efficient Carry Skip Adder and FIR filter Implementation

Vellingiri GOVINDARAJ, Ezhılazhagan CHENGUTTUVAN, Dhanasekar SUBRAMANIYAM

Assistant Professor, Department of Electronics and Communication Engineering, Dr NGP Institute of Technology, Coimbatore, 641048, India. see\_govinf@yahoo.co.in. Associate Professor ,Department of Electronics and Communication Engineering, Sri Eshwar College of Engineering, Coimbatore, 641048, India.

Received: 16.08.2022

Accepted: 07.12.2022

**Abstract:** Adders are used in processing units such as Arithmetic and Logic Units (ALUs) as an essential building block, and in many blocks of microprocessor chips critical path, adders occupy an important place. Hence reducing power, area and increasing the speed of adders are significantly important. This paper proposes a modified structure of Carry Skip Adder (CSKA) with a reduction in consumption of power and area without affecting the speed when compared with the conventional adder structures. In order to get better effectiveness of the modified CSKA by including concatenation, incrementation schemes, and variable latency for the proposed hybrid structure, which reduces the power utilized without affecting the operating speed of the adder. The modified structure. Experimental results show that the 32-bit implementation of the proposed adder has a significant power reduction of 42% and 38.3%, area reduction of 27%, and 18.3% with respect to Conventional CSKA adder with a little over ahead in delay. The proposed adder is used to implement a 5-tap FIR filter which shows a significant reduction in power consumption and area.

Keywords: Carry Skip Adder, Power Consumption, FIR, Binary to Excess Code convertor.

# 1. Introduction

Adders are a significant unit in ALU operation for improving the performance of the processors, i.e., increasing the speed and reducing the energy consumed considerably may affect the processor performance [1]. It is fascinating to accomplish high speed by utilizing low power/energy seems to be an excellent test for the inventors of general-purpose processors [2]. Anyone can select any type of adder among the different adder structures/families to reduce the power and increase the speed [3]. The additional adders with various delays, area, and consumption of power like Parallel Prefix Adders (PPAs), Ripple Carry Adder (RCA), Carry Select Adder (CSLA), Carry Increment Adder (CIA), etc. With reduced area and power consumption, the RCA is a modest structure but has the worst critical path delay [4]-[16]. CSLA has high speed, power consumption, and area is also increased compared with RCA [18]-[21]. The PPAs quickly generate carry similar to carry look-ahead adder. Based on the algorithms used and performance, the PPA structure is classified [22]. It has to be understood that the PPA structure has more complexities than any other adder structure, including the kogge stone adder [23]. The importance of power reduction of CMOS VLSI circuits is explained in [24]-[25]. The carry skip adder affords cooperation between an RCA and a CLA. The carry skip adder splits the words to be inserted into blocks. Inside each block, RCA produce carry

and sum bit [26]. Reduction in consumption of power and area usage, CSKA is considered an effective adder[27].

CSKA structure seems to have attractive features when compared to other adders. The proposed adder structure uses binary to excess-1 code converters (BEC) of n bit. The main advantage of using a BEC converter instead of RCA in the proposed adder is the area and power consumption are reduced without affecting the addition speed.

# 2. Existing Carry Skip Adder technique

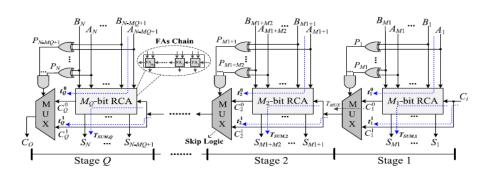

Figure 1 shows M-bit existing -CSKA Ripple carry adder in each stage.

Figure 1 Structure of M-bit Conventional CSKA [1]

Considering the process of the concatenation of full adders (FA) in every stage, there will be a skip in the carry logic. In RCA, there are N number of Full Adders connected having larger propagation delay for adding two M-bit numbers A and B, So the worst case delay is given by

$$P_i = A_i \oplus B_i \quad i=1,\dots,N \tag{1}$$

Pi is called propagate term, as shown in equation (1).

CSKA, in each stage, has to carry input in skip logic (multiplexer) and the carry output (FA chain) in the Ripple Carry Adder block. The propagation signals, which are used as the selection lines in the multiplexer, are generated at the product of each stage, as represented in figure 1. The fixed size stage(FSS) and variable size stage(VSS) are used to implement the CSKA, which produces high-speed operation for the VSS structure, and the stage size used is similar to the RCA block.

# 3. Proposed CSKA Structure

The CSKA is used in various computational framework designs to direct the propagation delay occurring due to carry, which is skipped to generate the sum over the carry blocks. Ripple carry adder independently (for Cin=1 and 0) is used by CSKA to produce the resulting sum. Nonetheless, the CSKA, which is normally used, doesn't enhance the features of area and speed because of using multiple combinations of RCA for generating fractional sum and carry by considering input carry. Multiplexers select the final carry and sum of CSKA. Therefore, by using two independent RCAs will increase the area and also leads to an increase in delay.

The problem said above can be addressed by using n-bit BEC converters. In CSKA, replacing RCA with BEC will provide lesser area usage and reduced delay, improving the addition process's speed. One advantage is fewer gates will be used than the FA structure, so the number of gates is

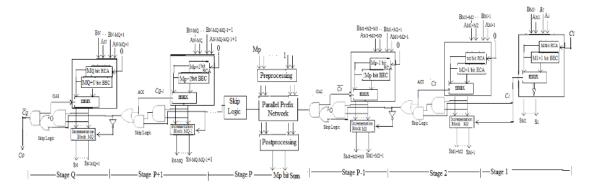

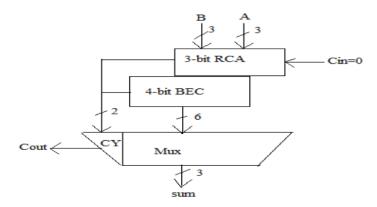

decreased. Figure 2 shows the proposed design of the 32-bit CSKA structure. This logic can be used to implement any adders in the modified design. Figure 3 represents the logic of 3-bit RCA with BEC.

Figure 2. Proposed adder circuit

Figure 3. 3-bit RCA With BEC

In regular CSKA structure, for 3-bit RCA, two independent RCA blocks for Cin=1 and Cin=0 are used. The proposed area-efficient CSKA uses the RCA block with BEC, as shown in figure 3. Here RCA logic is replaced with BEC logic.

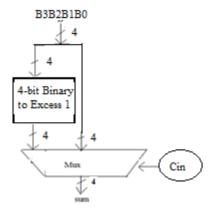

## 3.1 BEC concept

Figure 4. illustrates the basic function of the CSKA and its implementation using a multiplexer and 4-bit BEC. Two inputs are applied to multiplexer B0, B1, B2, and B3 are one set of inputs, and the output of BEC is the other set of inputs. The output of the multiplexer is selected by using Cin. Based on Cin's value, the multiplexer will select 4 bits, either B0 to B3 or the output of BEC. The main advantage of using Binary to Excess three Code converter is to reduce the number of transistors by area of the chip while designing a large number of CSKA adders.

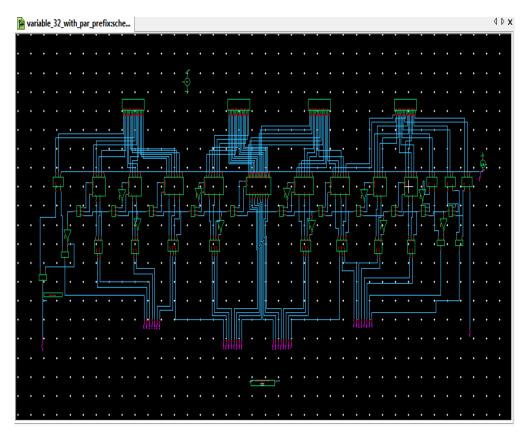

The carry skip adder's various structures are implemented using TANNER EDA software. The proposed implementations are shown in Figure 5.

Figure 4.BEC structure for 4 bit.

Figure 5. Structure of Proposed Adder using tanner tool.

### 4. Results and Discussion

Table 1 provides a proposed adder to the input patterns applied details. The sum and carry of the CSKA are generated by applying the inputs. TANNER EDA Tool is used for implementing the proposed adder, and power and delay were calculated. The number of transistors used determines the area occupied in this design. The comparison of Concatenation & Incrimination CSKA and hybrid variable latency CSKA with area efficient CSKA in terms of power, delay and area for the input pattern is given in Table 2.

Govindaraj V, Ezhilazhagn C, Dhanasekar S.

\_

| Table 1.1 Toposed adder input patterns |       |       |       |       |       |       |       |       |

|----------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| LSB to                                 | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

| <b>MSB Bits</b>                        |       |       |       |       |       |       |       |       |

| Α                                      | 10110 | 10110 | 10110 | 10110 | 10110 | 10110 | 10110 | 10110 |

| B                                      | 10110 | 10110 | 10110 | 10110 | 10110 | 10110 | 10110 | 10110 |

| LSB to                                 | 15    | 14    | 13    | 12    | 11    | 10    | 9     | 8     |

| <b>MSB Bits</b>                        |       |       |       |       |       |       |       |       |

| Α                                      | 10110 | 10110 | 10110 | 10110 | 10110 | 10110 | 10110 | 10110 |

| B                                      | 11111 | 11111 | 11111 | 11111 | 11111 | 11111 | 11111 | 11111 |

| LSB to                                 | 23    | 22    | 21    | 20    | 19    | 18    | 17    | 16    |

| MSB Bits                               |       |       |       |       |       |       |       |       |

| Α                                      | 10110 | 10110 | 10110 | 10010 | 10010 | 10010 | 10010 | 10010 |

| B                                      | 00000 | 00000 | 00000 | 00000 | 00000 | 00000 | 00000 | 00000 |

| LSB to                                 | 31    | 30    | 29    | 28    | 27    | 26    | 25    | 24    |

| <b>MSB Bits</b>                        |       |       |       |       |       |       |       |       |

| Α                                      | 00000 | 00000 | 00000 | 00000 | 00000 | 10110 | 10110 | 10110 |

| В                                      | 11001 | 11001 | 11001 | 11001 | 11001 | 11001 | 11001 | 11001 |

Table 1.Proposed adder input patterns

Table 2. Comparison among different structures for 32-bit

|                 | Structure of adders |      |          |  |

|-----------------|---------------------|------|----------|--|

|                 | CSK                 | CSKA | Proposed |  |

| Parameter       | Α                   | CI   | Adder    |  |

| Power(mW)       | 53.3                | 50.4 | 30.9     |  |

| Delay(ns)       | 43.6                | 43.7 | 43.9     |  |

| Area(transistor | 3270                | 2938 | 2386     |  |

| count)          |                     |      |          |  |

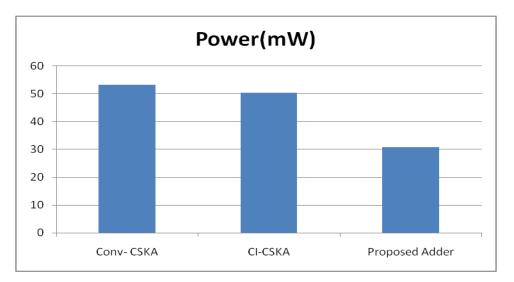

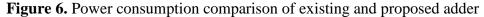

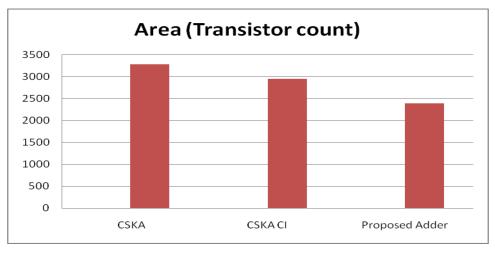

Table 2 compares the performance of CSKA, CSKACI, and the proposed adder. The proposed adder has a reduction in power consumption and area compared with the existing CSKA structures but with a slight increase in delay.

Figure 7. Delay comparison of conventional CSKA and proposed adder

Figure 8. Comparison of Area in transistor count

Figure 6 and Figure 8 show a comparison of power consumption and area of the existing method and proposed method in which the proposed adder power consumption and area are reasonably lower than the existing methods. Figure 7 shows the comparison of the delay of the existing method and the proposed method in which the proposed adder delay is slightly higher than the existing method.

#### 5. Implementation of FIR filter using proposed adder

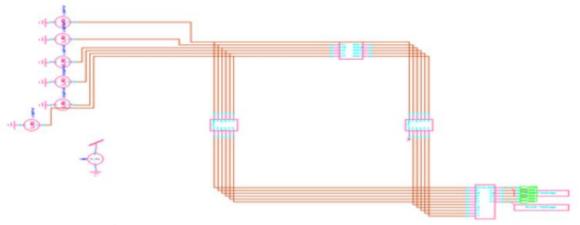

The proposed adder is used in the adder unit of FIR to design the 5-tap FIR filter. Figure 9 shows the schematic implementation of the 5-tap FIR filter.

Figure 9. Schematic of 5 tap FIR filter using proposed adder

| <b>Different structure</b> / | FIR Filter Using Existing CSKA | <b>Proposed adder</b> |

|------------------------------|--------------------------------|-----------------------|

| Parameter                    |                                |                       |

| Power(mw)                    | 0.194                          | 0.183                 |

| Area(Transistor count)       | 852                            | 840                   |

#

## 6. Conclusion

An area-efficient CSKA was proposed by modifying hybrid variable latency CSKA. It exploits the customized parallel adder model at the middle stage, which provides an opportunity to reduce the area and power consumed by using n-bit binary to excess-1 code converters (BEC). Comparing the proposed method with the existing method, the proposed method has a slight increase in delay with a significant reduction in power and area. The proposed adder size of 32-bit is implemented using the tanner tool, and a comparison of results shows considerable power reduction of 42% and 38.3%. area reduction of 27% and 18.3% for conventional CSKA and CI CSKA adder with a little over ahead in delay. The over ahead is delayed due to additional logic circuits. The proposed adder shows a power reduction of 7.4% percentage and the area in the number of transistors is 1.4% while using the proposed adder to implement a 5-tap FIR filter.

#### Acknowledgments

This work was not supported by any funding agency

#### Authors' contributions

VG,CE and SD designed the the adder structure. VG implemented the structure in EDA tool. VG carried out simulation work, implemeted the FIR structure using adders, in collaboration with CE and SD, VG,CE and SD wrote up the article.

All the authors read and approved the final manuscript.

# **Competing interests**

The authors declare that they have no competing interests.

## References

- [1]. Alioto, M. and Palumbo, G., "A simple strategy for optimized design of one-level carry- skip adders", IEEE Trans. Circuits Syst. I, Fundam. Theory Appl, 2002, 50(1): 141-148.

- [2]. Chen, Y., "Variable-latency adder (VL-adder) design for low power and NBTI tolerance", IEEE Trans. Very Large Scale Integr. (VLSI) Syst, 2010, 18(11): 1621-1624.

- [3]. Chen, Y., Li, H., Li, J., and Koh, C, K., "Variable-latency adder (VL-adder): New arithmetic circuit design practice to overcome NBTI", ACM/IEEE Int. Symp. Low Power Electron. Design (ISLPED), 195-200, (2007).

- [4]. Chirca, K., "A static low-power, high-performance 32-bit carry skip adder", in Proc. Euromicro Symp. Digit. Syst. Design (DSD), 615-619, (2004).

- [5]. Gayles, E., Owens, R. M. and Irwin, M. J., "Low power circuit techniques for fast carry- skip adders", Proc. Midwest Symp. Circuits and Systems, 87-90, (1996).

- [6]. Ghosh, S. and Kaushik, R., "Exploring high-speed low-power hybrid arithmetic units at scaled supply and adaptive clock-stretching", in Proc. Asia South Pacific Design Autom. Conf. (ASPDAC), 635-640, (1996).

- [7]. Guyot, A., Hochet, B., and Muller, J. M., "A way to build efficient carry skip adders", IEEE Trans. Comput., 2008, 36(10): 1144-1152.

- [8]. Harris, D., "A taxonomy of parallel prefix networks", in Proc. IEEE Conf.Rec. 37th Asilomar Conf. Signals, Syst., Comput, 2: 2213-2217, (1987).

- [9]. Jia, S., "Static CMOS implementation of logarithmic skip adder", in Proc. IEEE Conf. Electron Devices Solid-State Circuits, 509-512, (2003).

- [10]. Kim, Y. and Kim, L. S., "64-bit carry-select adder with the reduced area", Electron. Lett, 2003, 37(10): 614-615.

- [11]. Kogge, P., M. and Stone, H. S., "A parallel algorithm for the efficient solution of a general class of recurrence equations", IEEE Trans. Comput, 2001, 22( 8): 786-793.

- [12]. Lehman, M. and Burla, N., "Skip techniques for high-speed carry propagation in binary arithmetic units", IRE Trans. Electron. Comput, 1073, 10(4): 691-698.

- [13]. Majerski, S., "On the determination of optimal distributions of carry skips in adders", IEEE Trans. Electron. Comput, 1967, 16(1): 45-58.

- [14]. Bahadori, M. Kamal, M. Afzali-Kusha, A. and Pedram, M., "High-Speed and Energy-Efficient Carry Skip Adder Operating Under a Wide Range of Supply Voltage Levels", IEEE transactions on Very Large Scale Integration (VLSI) systems, 2015, 24(2): 421-433.

- [15]. Nagendra, C. Irwin, M. J. and Owens, R. M., "Area-time-power tradeoffs in parallel adders", IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process, 1996, 43(10): 689-702.

- [16]. Oklobdzija, V. G., Zeydel, B. R., Dao, H. Q., Mathew, S. and Krishnamurthy, R., "Comparison of high-performance VLSI adders in the energy-delay space", IEEE Trans. Very Large Scale Integr. (VLSI) Syst, 2005, 13(6): 754-758.

- [17]. Parhami, B., "Computer Arithmetic Algorithms and Hardware Designs", Oxford Univ. Press.

- [18]. Ramkumar, B. and Kittur, H. M., "Low-Power and Area-Efficient Carry Select Adder", IEEE Transactions On Very Large Scale Integration (VLSI) Systems, 2012, 20(2): 371-375.

- [19]. Ramkumar, B. and Kittur, H. M. and Kannan, P. M., "ASIC implementation of modified faster carry save adder", Eur. J. Sci. Res, 2010, 42(1): 53-58.

- [20]. Sakshi, R. Gitanjali, P. S. and Garima., "Design of low power and high-speed BEC 2248 efficient novel carry select adder", International Journal of Advances in Engineering & Technology, 2013, 6(1): 172-178.

- [21]. Turrini, S., "Optimal group distribution in carry-skip adders", in Proc.9th IEEE Symp. Comput. Arithmetic, 96-103, (1989).

- [22]. Zlatanovici, R., Kao, S. and Nikolic, B., "Energy-delay optimization of 64-bit carrylookahead adders with a 240 ps 90 nm CMOS design example", IEEE J. Solid-State Circuits, 2006, 44(2): 569-583.

- [23]. Govindaraj, V. and Ramesh, J., "An Improved Low Transition Test Pattern Generator for Low Power Applications", Design Automation for Embedded Systems, 2017, 21(3): 247-263.

- [24]. Govindaraj, V. and Aruna Devi, B., "Machine learning based power estimation method for CMOS VLSI circuits", Applied Artificial Intelligence, 2021, 35(13): 1043-1055.

- [25]. Govindaraj, V., Manoharan, K., Prabha, L., Dhanasekar, S., and Sreekanth, K., "Minimum Power Test Pattern Generator for Testing VLSI Circuits", 6th International Conference on Devices, Circuits and Systems (ICDCS), 2022, 27-31, DOI:10.1109/ICDCS54290.2022.9780773.

- [26]. Dubey, S., Verma, G., "Analysis of Basic Adder with Parallel Prefix Adder", First IEEE International Conference on Measurement, Instrumentation, Control and Automation (ICMICA), 2020: 1-6, DOI: 10.1109/ICMICA48462.2020.9242842.

- [27]. Daniel Raj, A., Saravana Kumar, R. Sanjoy, Deb. Vignesh Roshan, M. Sugirdan, V. and Soundar, S., "Design and Analysis of High-Performance Carry Skip Adder using Various Full Adders", Smart Technologies, Communication and Robotics (STCR), 2021: 1-5, DOI: 10.1109/STCR51658.2021.9588863.