# NEW DXCCII-BASED GROUNDED SERIES INDUCTANCE SIMULATOR TOPOLOGIES

Abdullah YEŞİL<sup>1</sup> and Fırat KAÇAR<sup>1</sup>

<sup>1</sup>Department of Electrical and Electronics Engineering Istanbul University, Istanbul, Turkey E-mails: abdullah.yesil@istanbul.edu.tr, fkacar@istanbul.edu.tr

Abstract: In this paper, five grounded series inductance simulator topologies are proposed. All proposed circuits employing a minimum number of DXCCII and passive components. The proposed topologies realized all grounded parallel inductance variations. To demonstrate the performance of the presented DXCCII based parallel inductance simulators, we use one of the circuits to construct a current mode multifunction filter. Simulation results are given to confirm the theoretical analysis. The proposed DXCCII and its applications are simulated using CMOS 0.35 µm technology.

Keywords: : Analog MOS Integrated Circuit, inductance simulator, DXCCII

## 1. Introduction

Inductance simulators are very important building for analog filter circuits design. The advantage of integrated circuits has encouraged the design of synthetic inductances, which can be used instead of the bulky inductors in passive filters. Several grounded inductance simulator topologies have been reported in the literature [1]-[22]. These topologies can be classified based on the number of active and passive elements employed and whether they realize a lossy or lossless kind of inductance. However, many of these circuits require more than two active components and three or more passive elements for grounded inductance simulation. Most of these circuits employ two or more active elements to realize grounded inductance [3]-[5], [7]-[9], and [12]. The proposed topologies in [1], [6], [10], and [11] employ a single active element but they do not realize pure inductance. Although the circuit reported in [5] realizes pure inductance with only one positive type secondgeneration current conveyor (CCII+), it employs five passive elements. In comparison to previous DXCCII based inductor simulator circuit [17], the number of active element reduced by one.

In this paper, we propose grounded inductance simulator topologies employing a minimum number of active and passive components including one dual-x second generation current conveyor (DXCCII), two resistors, and one capacitor. The proposed topologies realized all grounded series inductance variations. Finally, the proposed circuit is tested in the currentmode multifunction filter. Simulations of the circuits by the SPICE program give results that agree well with the theoretical results.

Received on: 30.04.2013 Accepted on: 04.04.2014

## 2. Proposed Circuit

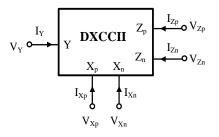

The circuit symbol of the dual-x current conveyor (DXCCII) is shown in Fig.1. It has two X terminals, namely  $X_p$  (non-inverting X terminal) and  $X_n$  (inverting X terminal). The  $X_p$  and  $X_n$  terminal currents are reflected to the respective Z terminals, namely  $Z_p$  and  $Z_n$  [23]. The Y terminal is high impedance terminal and  $X_p$ ,  $X_n$  terminals are low impedances. The  $Z_p$  and  $Z_n$  terminals are high impedance nodes suitable for current outputs.

Figure 1. The symbol of the DXCCII

Using standard notation, the port relations of an ideal DXCCII shown in Fig.1 can be characterized by

$$\begin{bmatrix} I_{Y} \\ V_{xp} \\ V_{xn} \\ I_{zp} \\ I_{zn} \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 \\ \beta_{1} & 0 & 0 \\ -\beta_{2} & 0 & 0 \\ 0 & \alpha_{p} & 0 \\ 0 & 0 & \pm \alpha_{n} \end{bmatrix} \begin{bmatrix} V_{Y} \\ I_{xp} \\ I_{xn} \end{bmatrix}$$

(1)

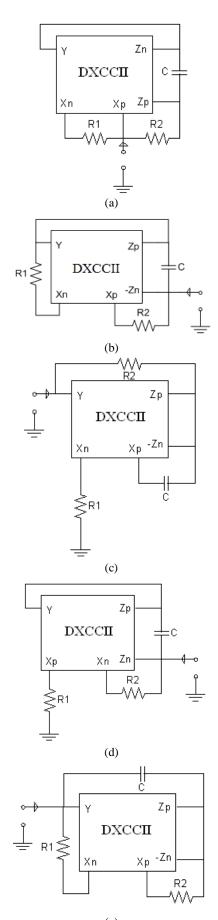

The proposed series lossless and lossy inductor simulators are given in Figs. 2a, 2b, 2c, 2d 2e. Routine analyses of the circuits in Figs. 2a-2e are given in Table 1. From Table 1 by comparison of various equations belonging to different circuits the following observations are possible: The circuit in Fig.2a and Fig.2b can simulate pure negative and positive inductance, respectively. The circuits which are shown in Fig.2b can simulate also series (+L) with (-R). Fig.2c circuit can simulate series (-L) with (-R). The circuit in Fig.2d. can simulate series (-L) with (+R). The last circuit in Fig.2e. can simulate series (+L) with (+R). Positive inductances can be used to implement filters. Negative inductances are especially important if the parasitics have to be cancelled.

$\alpha_p$ ,  $\alpha_n$ ,  $\beta_1$  and  $\beta_2$  are considered in the analysis of the proposed inductance simulator circuit in Fig. 2. Non-ideality analysis with current and voltage tracking errors taken into account are carried out for each circuit separately. Non-ideal equations for each circuit are given in Table.2.

| Circuit | Matching          | $\mathbf{Z}_{eq}$                                             | $\mathbf{L}_{\mathbf{eq}}$     | $\mathbf{R}_{eq}$        | Туре              |

|---------|-------------------|---------------------------------------------------------------|--------------------------------|--------------------------|-------------------|

| Fig. 2a | No                | $Z_{eq} = -\frac{sCR_1R_2}{4}$                                | $L_{eq} = -\frac{sCR_1R_2}{4}$ | -                        | Pure –L           |

| Fig. 2b | $R_1 = 2R_2 = 2R$ | $Z_{eq} = \frac{sCR_1R_2}{4} + \frac{R_2}{2} - \frac{R_1}{4}$ | $L_{eq} = \frac{sCRR}{2}$      | -                        | Pure L            |

| Fig. 2b | $R_1 = 4R_2 = 4R$ | $Z_{eq} = \frac{sCR_1R_2}{4} + \frac{R_2}{2} - \frac{R_1}{4}$ | $L_{eq} = sCRR$                | $R_{eq} = -\frac{R}{2}$  | L with series –R  |

| Fig. 2c | No                | $Z_{eq} = -2sCR_1R_2 - R_1$                                   | $L_{eq} = -2sCR_1R_2$          | $R_{eq} = -R_1$          | -L with series –R |

| Fig. 2d | $R_2 = 4R_1 = R$  | $Z_{eq} = \frac{-sCR_1R_2 + R_2}{2 + sC R_2 - 4R_1}$          | $L_{eq} = -\frac{sCRR}{8}$     | $R_{eq} = \frac{R}{2}$   | -L with series R  |

| Fig. 2e | No                | $Z_{eq} = \frac{sCR_1R_2}{4} + \frac{R_1}{2}$                 | $L_{eq} = \frac{sCR_1R_2}{4}$  | $R_{eq} = \frac{R_1}{2}$ | L with series R   |

Table 1. The actively realizable inductance forms.

Table 2. DXCCII-based grounded series inductance circuits for the non-ideal case

| Circuit | $\mathbf{Z}_{eq}$                                                                                                                                          | Matching                                                          |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| Fig. 2a | $\frac{sCR_1R_2\alpha_p\beta_1}{-\alpha_n \ 1+\alpha_p  \beta_1+\beta_2 \ +sC \ R_1 \ 1+\alpha_p  -1+\beta_1 \ -R_2 \ \alpha_n-\alpha_p  \beta_1+\beta_2}$ | No                                                                |

| Fig. 2b | $\frac{sCR_1R_2 + 2R_2 - R_1\alpha_p}{2 - 2sCR_2 - 1 + \alpha_n + 2\alpha_n\alpha_p}$                                                                      | $R_1 = R_2 \frac{2}{\alpha_p}$                                    |

| Fig. 2b | $\frac{sCR_1R_2 + 2R_2 - R_1\alpha_p}{2 - 2sCR_2 - 1 + \alpha_n + 2\alpha_n\alpha_p}$                                                                      | $R_1 = R_2 \frac{4}{\alpha_p}$                                    |

| Fig. 2c | $-\frac{sCR_1R_2 \ 1+\alpha_p \ +R_1}{sCR_1 \ 1+\alpha_p \ -1+\beta_1 \ +\alpha_n\beta_2}$                                                                 | No                                                                |

| Fig. 2d | $\frac{sCR_1R_2 - \alpha_p\beta_1R_2}{-1 + \alpha_n \ \alpha_p\beta_1 + sC \ -\alpha_p\beta_1R_2 + R_1 \ 1 + \alpha_n \ 1 + \beta_2}$                      | $R_2 = \frac{R_1 \ 1 + \alpha_n \ 1 + \beta_2}{\alpha_p \beta_1}$ |

| Fig. 2e | $\frac{sCR_1R_2 + R_1 \ 1 + \alpha_p}{-1 + \alpha_p \ 1 + \beta_2 \ + sC \ R_1 \ 1 + \alpha_p \ -1 + \beta_1 \ + R_2 \ -1 + \alpha_n \ 1 + \beta_2}$       | No                                                                |

(e) Figure 2. Inductance simulators realized using single DXCCII

#### **3. Simulations**

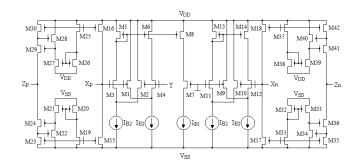

All of the circuits illustrated in Fig. 2 are tested with SPICE simulations. A possible CMOS realization of a DXCCII element is given in Fig.3. The cross-coupled quad configuration proposed by [24], shown in Fig.3, has superior linearity and input voltage range compared with conventional source-coupled differential pair. A high performance output stage, shown in Fig.3, is proposed by [25]. The two complementary current mirrors are composed of transistors M11-M24 and M25-M30. In the regulatedgate-cascade (RGC) parts [25] of the output stage high output impedance is achieved by the negative activefeedback loop along M22 and M28 the source follower M24 and M29. The series inductance configurations presented in this study are simulated using this CMOSbased DXCCII circuit. The supply voltages, are selected as  $V_{DD} = -V_{SS} = 1.5V$ . The aspect ratios of the transistors are given in Table 3. The MOS transistors are simulated using TSMC CMOS 0.35µm process model parameters.

Table 3. Transistors aspect ratios for the proposed circuit

| Transistors          | W(µm) | L(µm) |

|----------------------|-------|-------|

| M1-M4, M7, M9-M12    | 14    | 0.7   |

| M5, M6, M8, M13, M14 | 28    | 0.7   |

| M15, M17, M35-M36    | 21    | 0.7   |

| M23-M24              |       |       |

| M16, M18, M29, M30,  | 7     | 0.7   |

| M41,M42              |       |       |

| M19, M25, M31, M37   | 2.1   | 0.7   |

| M20-M21, M26-M27,    | 1.75  | 0.7   |

| M32-M33, M38-M39     |       |       |

| M34, M22, M28, M40   | 0.7   | 0.7   |

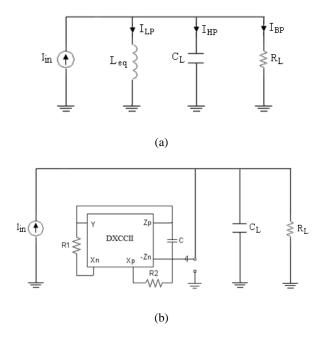

To demonstrate the accuracy of the topology proposed, the frequency responses of the impedances obtained from ideal and simulated circuits are calculated. Furthermore a current-mode multifunction filter was realized as an application example by connecting a parallel capacitor and resistor to the circuit illustrated in Fig.6b. In this Fig actively simulated inductance simulator circuit in Fig.2b replaces the parallel L circuit. The transfer functions are given by

$$\frac{I_{HP}}{I_{IN}} = \frac{s^2}{s^2 + s\frac{1}{C_L R_L} + \frac{1}{C_L L_{eq}}}$$

(2)

$$\frac{I_{BP}}{I_{IN}} = \frac{s \frac{1}{C_L R_L}}{s^2 + s \frac{1}{C_L R_L} + \frac{1}{C_L L_{eq}}}$$

(3)

$$\frac{I_{LP}}{I_{IN}} = \frac{\frac{1}{C_L L_{eq}}}{s^2 + s \frac{1}{C_L R_L} + \frac{1}{C_L L_{eq}}}$$

(4)

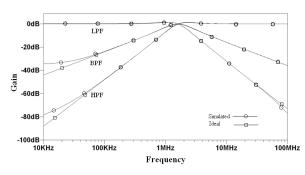

The element values of the realized filter are chosen as follows:  $C_L=0.1nF$ ,  $R_L=1k\Omega$ ,  $R_1=2R_2=2R=1k\Omega$  and C=0.8nF, thus an inductor with  $L_{eq}=0.1mH$  is obtained which result in a pole frequency  $f_p=1.59MHz$ . The designed filter circuit is simulated with PSPICE program using a CMOS realization of DXCCII shown in Fig 4. Simulated high-pass ( $I_{HP}$ ) low-pass ( $I_{LP}$ ) and band-pass ( $I_{BP}$ ) responses of the current-mode multifunction filter are given in Fig. 5.

Figure 4. a) Passive multifunction filter b) Multifunction filter constructed with DXCCII inductance simulator

Figure 5. Ideal and simulated high-pass, low-pass and bandpass responses of the current-mode multifunction filter

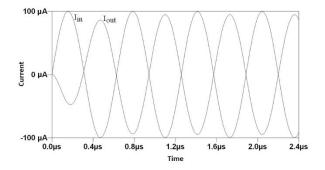

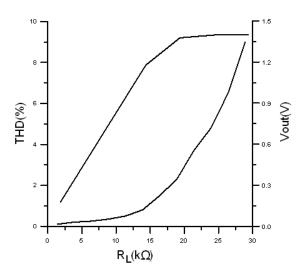

Time domain analysis result is given in Fig.6 for peak-topeak 100mV 1.59MHz sine wave input for band-pass filter configuration for the circuit in Fig 4b. Also in Fig.7, for an input signal of 100 $\mu$ A amplitude at 1MHz, variation of the THD value versus output load resistance is shown. For a load resistance lower than 20k, THD is low, less than 3%. Output amplitude change with load resistance for constant input signal is seen in Fig.7 it is seen that, at 1MHz frequency a large swing V<sub>0</sub>=1.43V is obtained at the output.

Figure 6. The input and output waveforms of the proposed bandpass filter of Fig. 4b for 1.59MHz sinusoidal input current of  $200\mu V$  (peak to peak).

**Figure 7.** Total harmonic distortion and dependence of the output amplitude versus load resistance for an input signal of 100µA amplitude at 1MHz.

#### 4. Conclusions

New single-DXCCII based lossless and lossy grounded series inductance simulation circuits have been presented. The proposed circuit employs a single DXCCII along with two resistors and a single capacitor. A second-order multifunction filter is realized to illustrate the practical uses of the proposed lossless inductor simulator as application example. The workability of the new circuit was demonstrated by using CMOS DXCCII known earlier [23]. Simulation results well confirm the theoretical analysis. With the availability of any off-the shelf IC DXCCII in future, the inductance simulation circuit proposed in this paper may find use in various analog signal processing signal/generation applications realizable with IC DXCCII.

### 5. References

- R., Senani "Active Simulation of Inductors Using Current Conveyors," *Electronics Lett.*, vol. 14, pp. 483-484, 1978.

- [2] A.N., Paul and D., Patranabis "Active Simulation of Grounded Inductors Using a Single Current Conveyor," *IEEE Trans. on Circuits and Systems*, vol. 28, pp. 164-165, 1981.

- [3] W.,Surakampontorn and P., Thitimajshima "Integrable Electronically Tunable Current Conveyors," *IEE Proc.*, Pt. G, vol. 135, pp. 71-77, 1988.

- [4] I.A., Khan, M.T., Ahmed and N., Minhaj "Novel Technique for Immitance Simulation–Realisation of Some All-Active Simulators," *Int'l J. of Electronics*, vol. 72, pp. 431-441, 1992.

- [5] C.L., Hou, R.D., Chen, Y.P., Wu, and P.C., Hu "Realization of Grounded and Floating Immitance Function Simulators Using Current Conveyors," *Int'l J. of Electronics*, vol. 74, pp. 917-923, 1993.

- [6] C.M., Chang, H.Y., Wang and C.C., Chien "Realization of Series Impedance Functions Using one CCII+," *Int'l J. of Electronics*, vol. 76, pp. 83-85, 1994.

- [7] S.I., Liu and C.Y., Yang "Higher-Order Immitance Function Synthesis Using CCIIIs," *Electronics Lett.*, vol. 32, pp. 2295-2296, 1996.

- [8] A., Fabre, H., Amrani and O., Saaid "Current-Mode Bandpass Filters with Q Magnification," *IEEE Trans. on Circuits and Systems-II*, vol. 43, pp. 839-842, 1996.

- [9] O., Çiçekoğlu "Active Simulation of Grounded Inductors with CCII+s and Grounded Passive Elements," *Int'l J. of Electronics*, vol. 85, pp. 455-462, 1998.

- [10] H., Kuntman, M., Gülsoy and O., Çiçekoğlu "Actively Simulated Grounded Lossy Inductors Using Third Generation Current Conveyors," *Microelectronics J.*, vol. 31, pp. 245-250, 2000

- [11] H.Y., Wang and C.T., Lee, "Systematic Synthesis of R-L and C-D Immitances Using CCIII, *Int'l J. of Electronics*, vol. 87, pp. 293-301, 2000.

- [12] G., Ferri and N., Guerrini "High-Valued Passive Element Simulation Using Low-Voltage Low-Power Current Conveyors for Fully Integrated Applications," *IEEE Trans. on Circuits and Systems-II*, vol. 48, pp. 405-409, 2001.

- [13] E., Yuce "Grounded inductor simulators with improved low frequency performances", *IEEE Transactions on Instrumentation and Measurement*, 57(5), 1079–1084, 2008.

- [14] M., Incekaraoglu and U.Cam, "Realization of series and parallel R-L and C-D impedances using single differential voltage current conveyor", Analog *Integrated Circuits and Signal Processing*, 43, 101–104, 2005.

- [15] E., Yuce and S., Minaei "A modified CFOA and its applications to simulated inductors, capacitance multipliers, and analog filters", IEEE Transactions

on Circuits and Systems I- Regular Papers, 55(1), 254–263, 2008.

- [16] E., Yuce "Novel lossless and lossy grounded inductor simulators consisting of a canonical number of components", Analog Integrated Circuits and Signal Processing, 59, 77-82, 2009.

- [17] A., Zeki and A., Toker "DXCCII-based tunable gyrator", International Journal of Electronics and Communications (AEÜ), 34(1), 59-62, 2005.

- [18] E., Yuce, O., Cicekoglu and S., Minaei, "CCII-based grounded to floating immittance converter and a floating inductance simulator", Analog Integrated Circuits and Signal Processing, 46, 287–291, 2006.

- [19] E., Yuce, S., Minaei and O., Cicekoglu "Novel floating inductance and FDNR simulators employing CCIIs", Journal of Circuits Systems and Computers, 15, 78–81, 2006.

- [20] I., Myderrizi, S., Minaei and E., Yuce "DXCCII-based grounded inductance simulators and filter applications" Microelectronics Journal, vol. 42, pp. 1074–1081, 2011.

- [21] B., Metin "Supplementary Inductance Simulator Topologies Employing Single DXCCII" Radioengineering, vol. 20, no. 3, 2011.

- [22] F., Kacar and A., Yesil, "Novel grounded parallel inductance simulators realization using a minimum number of active and passive components." Microelectronics Journal, vol. 41, no. 10, pp. 632-638 2010.

- [23] A., Zeki and A., Toker "The dual-X current conveyor (DXCCII): A new active device for tunable continuoustime filters", International Journal of Electronics, 89(12), 913-923, 2002.

- [24] A., Nedungadi and T. R., Viswanathan "Design of Linear transconductance elements," IEEE Transactions on Circuit Theory, vol. CAS-31, pp. 891-894, 1984.

- [25] A., Zeki and H., Kuntman "Accurate and high output impedance current mirror suitable for CMOS current output stages," ElectronicsLetters, vol. 33, pp. 1042-1043, 1997.

**Abdullah YEŞİL** received B.Sc. and M.Sc. degree from Istanbul University in Electrical and Electronics Engineering in 2009 and 2011, respectively. He is now a Ph.D. student, also a research and teaching assistant in Istanbul University. His main research interests are active network synthesis and electronic circuits for computer aided design.

**Firat KAÇAR** received his B.Sc., M.Sc. and Ph.D.degrees from Istanbul University, all in Electrical and Electronics Engineering 1998, 2001 and 2005. He is currently an associate professor at the Electrical and Electronics Engineering Department of Istanbul University. His current research interests include analog circuits, active filters, synthetic inductors, CMOS based circuits electronic device modeling and hot-carrier effect on MOS transistor. He is the author or co-author of about 60 papers published in scientific journals or conference proceedings.